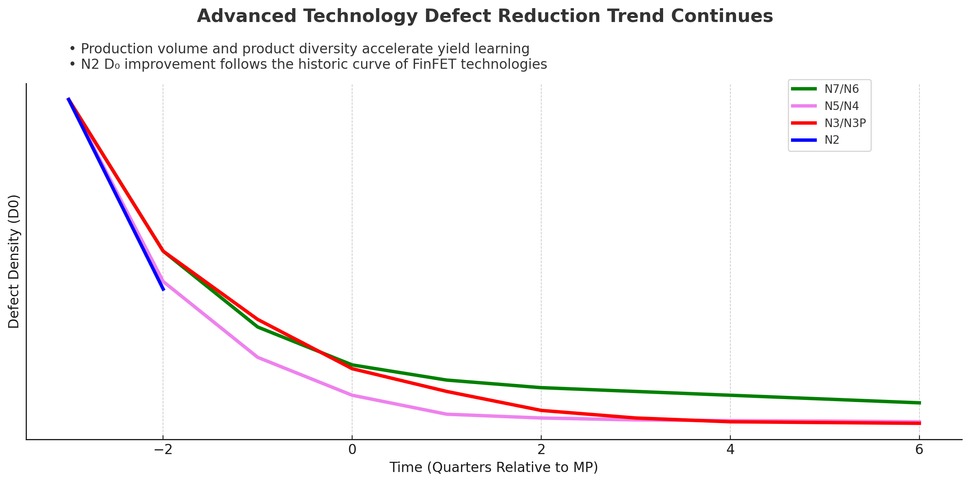

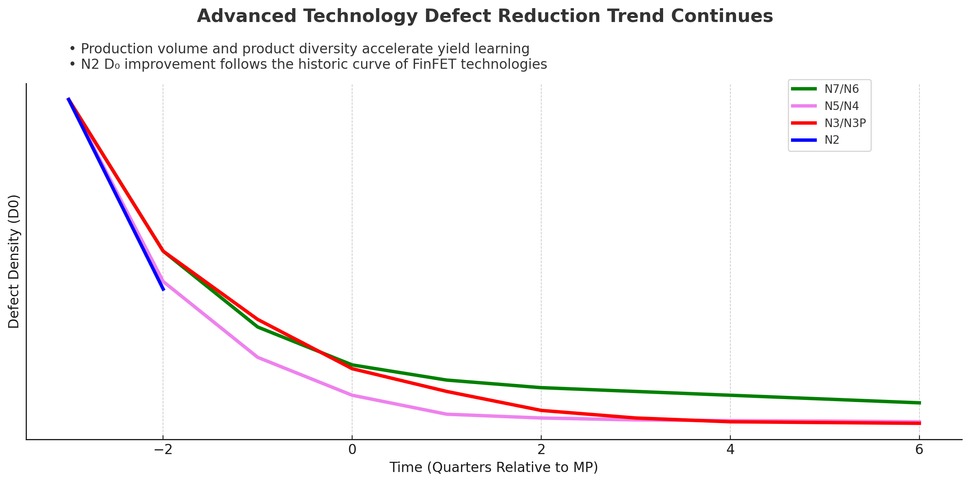

TSMC anunció recientemente en un seminario de tecnología de América del Norte la densidad de defectos (D0) de su tecnología de proceso N2 (2NM) en comparación con sus procesos predecesores en la misma etapa.Según la compañía, la densidad de defectos del proceso N2 es menor que la de los nodos de fabricación N3 (3NM), N5 (5 nm) y N7 (7 nm).Además, la diapositiva muestra que el proceso N2 de TSMC todavía está a dos cuartos de la producción en masa, lo que significa que se espera que TSMC comience a producir chips de 2NM a fines del cuarto trimestre de 2025 como se esperaba.

Aunque el proceso N2 de TSMC es la primera tecnología de proceso de la compañía para adoptar transistores de nanocotes de anillo de puerta completo (GAA), la densidad de defectos de este nodo es menor que el proceso de generación anterior en la misma etapa, dos cuartos por delante de la producción en masa (MP).Los procesos de generación anterior: N3/N3p, N5/N4 y N7/N6- todos usaron transistores de efectos de campo de aleta maduros (FINFET).Por lo tanto, aunque N2 es el primer nodo de TSMC en adoptar transistores de nanocuencias GAA, su reducción de densidad de defectos es mayor que el proceso de generación anterior antes de ingresar el hito de producción de masas (HVM).

Este cuadro representa la variación de la densidad de defectos con el tiempo, que abarca desde tres cuartos antes de la producción en masa a seis cuartos después de la producción en masa.Entre todos los nodos mostrados: la densidad de defectos N7/N6 (verde), N5/N4 (púrpura), N3/N3p (rojo) y N2 (azul) - disminuye significativamente el aumento del rendimiento, pero la tasa de disminución varía dependiendo de la complejidad de los nodos.Vale la pena señalar que N5/N4 es el más activo para reducir los defectos tempranos, mientras que la mejora del rendimiento de N7/N6 es relativamente suave.El nivel de defecto inicial de la curva N2 es más alto que el de N5/N4, pero luego disminuye bruscamente, lo que está muy cerca de la trayectoria de reducción de defectos de N3/N3p.

La diapositiva enfatiza que el rendimiento y la diversidad de productos siguen siendo factores impulsores clave para acelerar la mejora de la densidad de defectos.Una mayor producción y productos diversificados que utilizan el mismo proceso pueden identificar y corregir la densidad de defectos y producir problemas más rápido, lo que permite a TSMC optimizar los ciclos de aprendizaje de defectos.TSMC declaró que su tecnología de fabricación N2 ha obtenido más chips nuevos que su tecnología predecesora (ya que TSMC ahora produce chips N2 para teléfonos inteligentes y clientes de informática de alto rendimiento (HPC) en riesgo), y la curva de disminución de la densidad de defectos lo confirma básicamente.

Teniendo en cuenta los factores de riesgo provocados por la introducción de una nueva arquitectura de transistores, es particularmente importante que la tasa de reducción de defectos de N2 permanezca consistente con los nodos anteriores basados en FINFET.Esto indica que TSMC ha transferido con éxito su experiencia en el proceso de aprendizaje y gestión de defectos a la nueva era GAAFET sin encontrar contratiempos significativos.

RFQs/Orden (0)

RFQs/Orden (0)

RFQs/Orden (0)

RFQs/Orden (0)