Sensors

#### **Edition 2011-03**

Published by Infineon Technologies AG 81726 Munich, Germany © 2011 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

Revision History: 2011-03, V2.0

**Previous Revision: V1.0**

| Page    | Subjects (major changes since last revision)                            |

|---------|-------------------------------------------------------------------------|

| 6       | Ordering code updated                                                   |

| 7       | Section 1.2 updated                                                     |

| 14      | Table 3, supply voltage and magnetic induction expanded; figure 7 added |

| 15      | Table 4; notes of supply current expanded                               |

| 16      | Table 5; table 6 added                                                  |

| 17      | Table 7, ESD expanded                                                   |

| 21      | Table 10, Notes updated                                                 |

| 27      | Table 14, register 0x0D updated                                         |

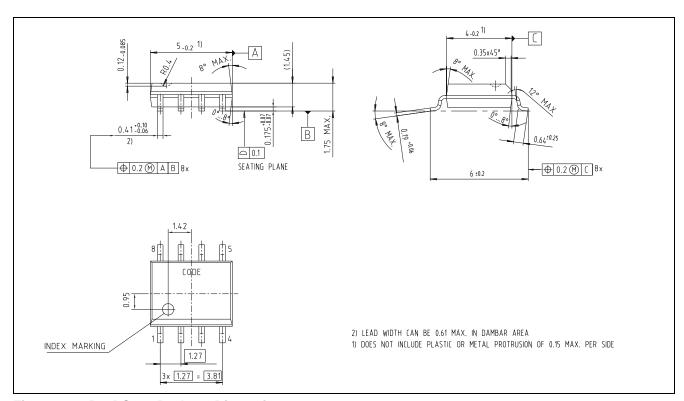

| 42      | Package outline in figure 23 modified                                   |

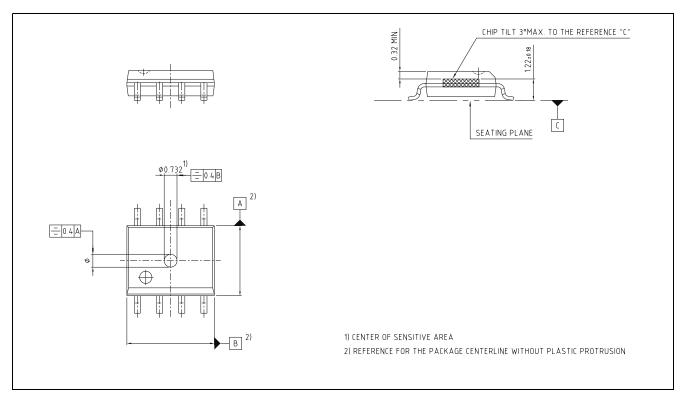

| 43      | Figure 24 added                                                         |

| general | Spelling and typing errors                                              |

## We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continously improve the quality of this document.

Please send your proposal (including a reference to this document) to:

sensors@infineon.com

### **Table of Contents**

# **Table of Contents**

|       | Table of Contents                                | 4    |

|-------|--------------------------------------------------|------|

| 1     | Product Description                              | 6    |

| 1.1   | Overview                                         | 6    |

| 1.2   | Features                                         | 7    |

| 1.3   | Application Example                              | 7    |

| 2     | Functional Description                           | ۶    |

| 2.1   | General                                          |      |

| 2.2   | Pin Configuration                                |      |

| 2.3   | Pin Description                                  |      |

| 2.4   | Block Diagram                                    |      |

| 2.5   | Functional Block Description                     |      |

| 2.5.1 | Internal Power Supply                            |      |

| 2.5.1 | GMR Voltage Regulator VRG (VDDG-Voltage)         |      |

| 2.5.2 | Analog Voltage Regulator VRA (VDDA-Voltage)      |      |

| 2.5.4 | Digital Voltage Regulator VRD (VDDD-Voltage)     |      |

| 2.5.4 |                                                  |      |

| 2.5.6 | Phase-Locked Loop (PLL)                          |      |

| 2.5.0 | Safety Features                                  |      |

| 3     | Specification                                    |      |

| 3.1   | Application Circuit                              |      |

| 3.2   | Absolute Maximum Ratings                         |      |

| 3.3   | Operating Range                                  | . 14 |

| 3.4   | Characteristics                                  | . 15 |

| 3.4.1 | Electrical Parameters                            | . 15 |

| 3.4.2 | ESD Protection                                   | . 17 |

| 3.4.3 | GMR Parameters                                   | . 17 |

|       | Offset and Amplitude                             | . 17 |

|       | Offset Definition                                | . 18 |

|       | Amplitude Definition                             | . 18 |

|       | Temperature-dependent behavior                   | . 18 |

|       | Orthogonality Definition                         | . 18 |

| 3.5   | Calibration                                      | . 19 |

|       | GMR Values                                       | . 19 |

|       | Temperature Measurement                          | . 19 |

|       | Calibration Conditions                           | . 19 |

| 3.6   | Angle Calculation                                | . 19 |

| 3.6.1 | Components of the Output Signals                 | . 19 |

| 3.6.2 | GMR Error Compensation                           | . 19 |

|       | Temperature-dependent Offset Value               | . 19 |

|       | Offset Correction                                | . 20 |

|       | Amplitude Normalization                          | . 20 |

|       | Non-Orthogonality Correction                     | . 20 |

|       | Resulting Angle                                  | . 20 |

| 3.6.3 | GMR Parameters after Calibration                 | . 21 |

| 3.7   | Signal Processing                                | . 21 |

| 3.8   | Clock Supply (CLK Timing Definition)             |      |

| 3.9   | Synchronous Serial Communication Interface (SSC) | . 22 |

| 3.9.1 | SSC Timing Definition                            |      |

|       | SSC Timing Diagram                               | . 23 |

### **Table of Contents**

| 3.9.2  | SSC Baud rate                                                    | 25 |

|--------|------------------------------------------------------------------|----|

| 3.9.3  | SSC Spike Filter                                                 |    |

| 0.0.0  | SSC Spike Filter Off                                             |    |

|        | SSC Spike Filter On                                              |    |

|        | Filter for DATA and CS                                           |    |

| 3.9.4  | SSC Data Transfer                                                |    |

| 3.9.5  | SSC Command Byte                                                 |    |

| 0.0.0  | Register Table                                                   |    |

|        | Bit Types                                                        |    |

|        | Reserved Registers (08 <sub>H</sub> to 0B <sub>H</sub> )         |    |

| 3.9.6  | Data Communication via SSC                                       |    |

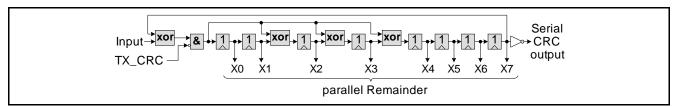

| 3.9.7  | CRC Generation                                                   |    |

| 3.9.8  | Slave-active Byte Generation                                     |    |

| 0.0.0  | Example1: CRC calculation (Update X and Y and set ADC-Test Mode) |    |

|        | Example 2: Use of two TLE5011 units in a bus mode.               |    |

| 3.10   | Test Structures                                                  |    |

| 3.10.1 | Functional Angle Tests                                           |    |

| 0      | ADC Test Vectors                                                 |    |

| 3.10.2 | Temperature Measurement                                          |    |

| 3.10.3 | Functional Angle Test and Temperature Measurement Timing         |    |

| 3.11   | Overvoltage Comparators                                          |    |

| 3.11.1 | Internal Supply Voltage Comparators                              |    |

| 3.11.2 | V <sub>DD</sub> Overvoltage Detection                            |    |

| 3.11.3 | GND-off Comparator                                               |    |

| 3.11.4 | V <sub>DD</sub> - off Comparator                                 |    |

|        |                                                                  |    |

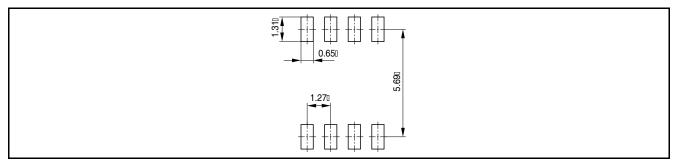

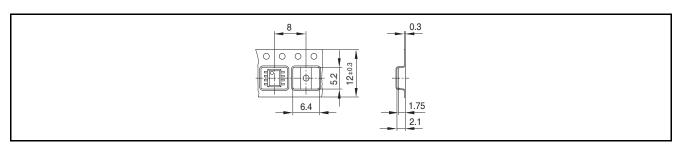

| 4      | Package Information                                              |    |

| 4.1    | Package Parameters                                               |    |

|        | Package Outline PG-DSO-8                                         |    |

|        | Footprint PG-DSO-8                                               |    |

|        | Packing                                                          |    |

|        | Marking                                                          |    |

|        | Processing                                                       | 44 |

GMR Angle Sensor TLE5011

## 1 Product Description

#### 1.1 Overview

The TLE5011 is a 360° angle sensor that detects the orientation of a magnetic field by measuring sine and cosine angle components with monolithic integrated **G**iant **M**agneto **R**esistance (**iGMR**) elements.

Data communications are accomplished with a bi-directional **S**ynchronous **S**erial **C**ommunication (**SSC**) interface that is SPI compatible.

The sine and cosine values can be read out digitally. These signals can be digitally processed to calculate the angle orientation of the magnetic field (magnet). This calculation can be done by using a **CO**ordinate **Rotation Digital Computer (CORDIC)** algorithm.

It is possible to connect more than one TLE5011 to one SSC interface of a microcontroller for redundancy or any other reason. If multiple TLE5011 devices are used, the synchronization of the connected TLE5011 is performed by a broadcast command.

Each connected TLE5011 can be addressed by a dedicated Chip Select CS pin.

| Туре    | Marking | Ordering Code | Package  |

|---------|---------|---------------|----------|

| TLE5011 | 5011    | SP000857850   | PG-DSO-8 |

**Product Description**

#### 1.2 Features

- Giant Magneto Resistance (GMR)-based principle

- Integrated magnetic field sensing for angle measurement

- Designed for 3.3 V and 5 V systems

- Full 0 360° angle measurement

- Highly accurate single-bit SD-ADC

- 16-bit representation of sine / cosine values on the interface

- Wide magnetic operating range: 30mT to 50mT

- · Bi-directional SSC interface up to 2 Mbit/s

- 3-pin SSC interface, SPI compatible with open drain

- ADCs and filters synchronized with external commands via SSC

- · Test resistors for simulating angle values

- Core supply voltage 2.5 V

- 0.25-µm CMOS technology

- Automotive qualified: -40°C to +150°C (junction temperature)

- Latch-up immunity according JEDEC standard

- ESD > 4 kV (HBM)

- · Green package with lead-free (Pb-free) plating

#### 1.3 Application Example

The TLE5011 GMR angle sensor is designed for angular position sensing in automotive applications, such as:

- Steering angle

- Brushless DC motor commutation (e.g. Electric Power Steering (EPS))

- Rotary switch

- General angular sensing

## 2 Functional Description

#### 2.1 General

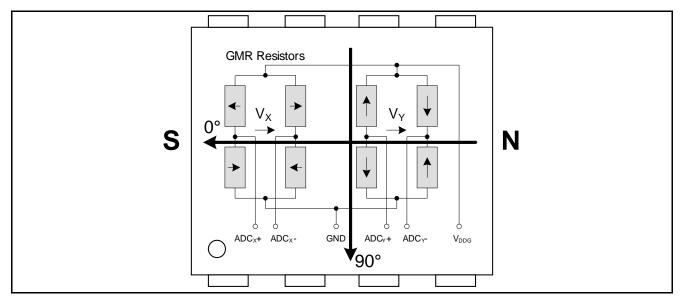

The GMR angle sensor is implemented in vertical integration. This means that the GMR active areas are integrated above the logic portion of the TLE5011 device. GMR elements change their resistance depending on the direction of the magnetic field.

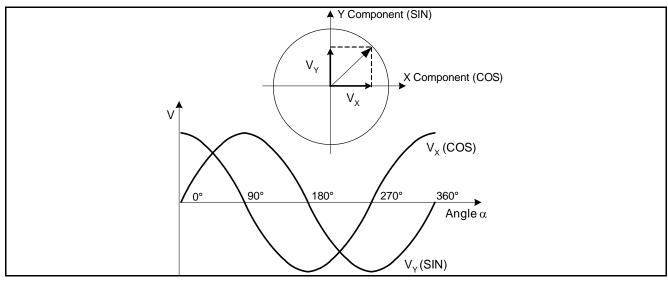

Four individual GMR elements are connected to one Wheatstone sensor bridge. These GMR elements sense either of two components of the applied magnetic field:

- X component, V<sub>X</sub> (cosine)

- Y component, V<sub>Y</sub> (sine)

The advantage of a full-bridge structure is that the amplitude of the GMR signal is doubled.

Figure 1 Sensitive Bridges of the GMR Angle Sensor

Note: In **Figure 1**, the arrows in the resistor symbols denote the direction of the reference layer, which is used for the further explanation (**Figure 2**).

The output signal of each bridge is only unambiguous over 180° between two maxima. Therefore two bridges are orientated orthogonally to each other to measure the 360° angle range.

Using the ARCTAN function, the true 360° angle value can be calculated that is represented by the relation of the cosine (here X) and sine (here Y) signals.

Because only the relative values influence the result, the absolute size of the two signals is of minor importance. Therefore, most influences on the amplitudes are compensated.

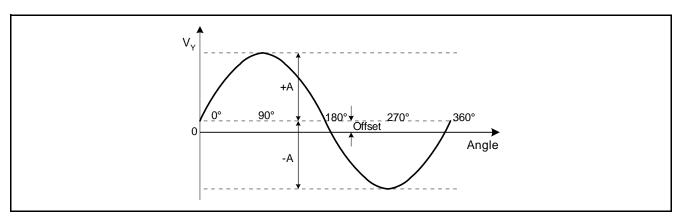

Figure 2 Ideal Output of the GMR Angle Sensor

## 2.2 Pin Configuration

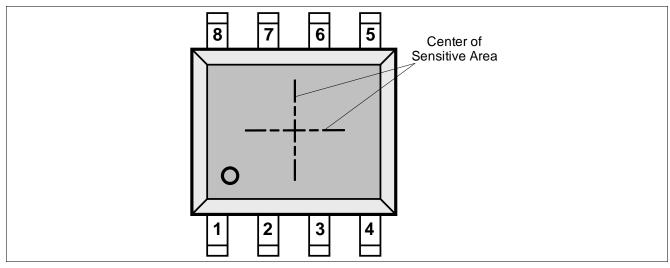

Figure 3 Pin Configuration (Top View)

## 2.3 Pin Description

Table 1 Pin Describtion

| Pin No. | Symbol   | In/Out | Function                             |

|---------|----------|--------|--------------------------------------|

| 1       | CLK      | I      | Chip Clock                           |

| 2       | SCK      | I      | SSC Clock                            |

| 3       | CS       | I      | SSC Chip Select                      |

| 4       | DATA     | I/O    | SSC Data, open drain                 |

| 5       | TST1     | I/O    | Test Pin 1, must be connected to GND |

| 6       | $V_{DD}$ | -      | Supply Voltage                       |

| 7       | GND      | -      | Ground                               |

| 8       | TST2     | I/O    | Test Pin 2, must be connected to GND |

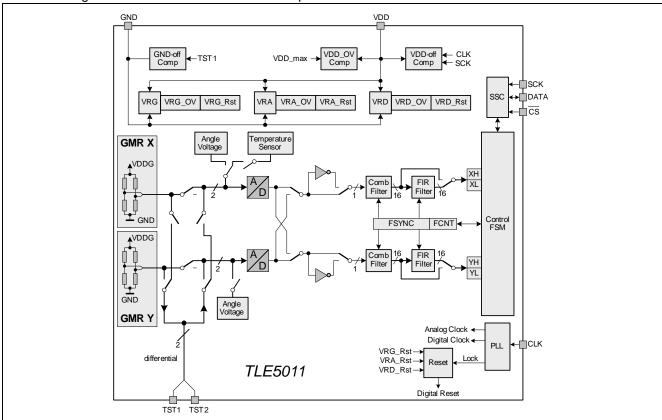

## 2.4 Block Diagram

The block diagram shows all switches in the reset position.

Figure 4 Block Diagram

### 2.5 Functional Block Description

#### 2.5.1 Internal Power Supply

The internal stages of the TLE5011 are supplied with different voltage regulators:

- GMR Voltage Regulator VRG

- Analog Voltage Regulator VRA

- Digital Voltage Regulator VRD

Each voltage regulator has its own overvoltage and undervoltage detection circuits.

#### 2.5.2 GMR Voltage Regulator VRG (VDDG-Voltage)

The GMR voltage regulator supplies all GMR parts:

- GMR bridges

- · Test voltages for angle test

- ADC reference voltage

The voltages are monitored in the VRG overvoltage and undervoltage detectors.

## 2.5.3 Analog Voltage Regulator VRA (VDDA-Voltage)

The analog voltage regulator supplies the analog parts:

- ADCs

- PLL (analog)

- VDD-off comparator

- GND-off comparator

- V<sub>DD</sub> Overvoltage detection

The voltages are monitored in the VRA overvoltage and undervoltage detectors.

#### 2.5.4 Digital Voltage Regulator VRD (VDDD-Voltage)

The digital voltage regulator supplies all digital parts:

- · Comb filters, FIR filters

- PLL (digital)

- Control FSM with bitmap

- SSC interface

- Counters (Reset, FSYNC, FCNT)

The voltages are monitored in the VRD overvoltage and undervoltage detectors.

### 2.5.5 Phase-Locked Loop (PLL)

The clock for the sensors is provided externally. This ensures synchronous operation in case of multiple system participants.

The sensor has its own PLL to generate the necessary clock frequency for the chip operation.

### 2.5.6 Safety Features

The TLE5011 has a multiplicity on safety features to support Safety Integrity Level (SIL). Sensors meeting this performance standard are identified by Infineon with the following logo:

Figure 5 PRO SIL Logo

Safety features are:

- Angle test (generated via test voltages feeding the ADC).

- Crossed signal paths (switchable for comparison)

- Invertable ADC bitstreams

- Overvoltage and undervoltage detection of internal and external voltages

- V<sub>DD</sub>-off and GND-off to detect supply malfunctions

- Frame counter and synchronisation counter

- Separate bandgap-reference voltages for regulators and comparators

- CRC-protected SSC protocol

- Locked configuration registers

#### **Disclaimer**

PRO-SIL™ is a Registered Trademark of Infineon Technologies AG

The PRO-SIL™ Trademark designates Infineon products which contain SIL Supporting Features.

SIL Supporting Features are intended to support the overall System Design to reach the desired SIL (according to IEC61508) or A-SIL (according to ISO26262) level for the Safety System with high efficiency.

SIL respectively A-SIL certification for such a System has to be reached on system level by the System Responsible at an accredited Certification Authority.

SIL stands for Safety Integrity Level (according to IEC 61508)

A-SIL stands for Automotive-Safety Integrity Level (according to ISO 26262)

# 3 Specification

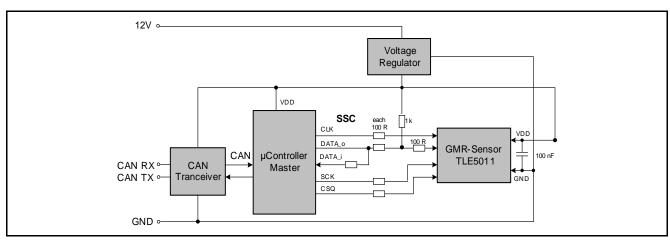

### 3.1 Application Circuit

The application circuit shows the microcontroller version with open-drain capabilities.

Figure 6 Application Circuit

A complete system may consist of one TLE5011 and a microcontroller. The second TLE5011 may be used for redundancy to increase system reliability. The microcontroller should contain a CORDIC coprocessor for fast angle calculations, and flash memory for the calibration data storage.

### 3.2 Absolute Maximum Ratings

Table 2 Absolute Maximum Rating Parameters

| Parameter                                                                                                                 | Symbol   | Lim  | it Values | Unit | Notes                                            |

|---------------------------------------------------------------------------------------------------------------------------|----------|------|-----------|------|--------------------------------------------------|

|                                                                                                                           |          | min. | max.      |      |                                                  |

| $\begin{tabular}{lll} \hline & Voltage on $V_{\rm DD}$ pin with respect to ground ($V_{\rm SS}$) \\ \hline \end{tabular}$ | $V_{DD}$ | -0.5 | 6.5       | V    | max 40 h / lifetime                              |

| Voltage on any pin with respect to ground (V <sub>SS</sub> )                                                              | $V_{IN}$ | -0.5 | 6.5       | V    | $V_{\rm DD}$ + 0.5 V may not be exceeded         |

| Junction temperature                                                                                                      | $T_{J}$  | -40  | 150       | °C   |                                                  |

|                                                                                                                           |          |      | 150       | °C   | for 1000 h not additive                          |

| Magnetic field induction                                                                                                  | В        | -    | 125       | mT   | max 5 min. @ T <sub>A</sub> = 25°C               |

|                                                                                                                           |          | -    | 100       |      | max 5 h @ T <sub>A</sub> = 25°C                  |

|                                                                                                                           |          | -    | 70        |      | max 1000 h @ $T_A = 85$ °C not additive          |

|                                                                                                                           |          | -    | [60]      |      | max 1000 h @ T <sub>A</sub> = 100°C not additive |

| Storage temperature                                                                                                       | $T_{ST}$ | -40  | 150       | °C   | without magnetic field                           |

Note: Stresses above the max. values listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

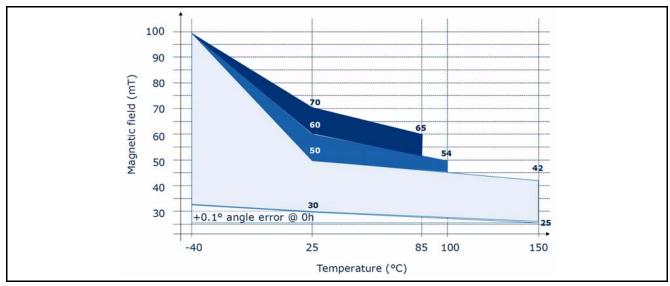

## 3.3 Operating Range

To ensure correct operation of the TLE5011, the operating conditions identified in **Table 3** must not be exceeded. All parameters specified in the following sections refer to these operating conditions, unless otherwise indicated. **Table 3** is valid for -40°C <  $T_J$  < 150°C

Table 3 Operating Range

| Parameter                                          | Symbol          | Limit Values |      |      | Unit | Notes                                     |

|----------------------------------------------------|-----------------|--------------|------|------|------|-------------------------------------------|

|                                                    |                 | min.         | typ. | max. |      |                                           |

| Supply Voltage                                     | $V_{DD}$        | 3.0          | -    | 5.5  | V    | For 3.3 & 5.0V systems <sup>1)</sup>      |

| Output Current                                     | $I_{Q}$         | -            | -5   | -10  | mA   | 2) 3)                                     |

| Input Voltage                                      | $V_{IN}$        | -0.3         | -    | 5.5  | V    | $V_{\rm DD}$ + 0.35 V may not be exceeded |

| Magnetic Induction at                              | B <sub>XY</sub> | 30           | -    | 50   | mT   | -40°C < T <sub>J</sub> <150°C             |

| $T_{A}$ = 25°C <sup>4) 5)</sup>                    | B <sub>XY</sub> | 30           | -    | 60   | mT   | -40°C < T <sub>J</sub> <100°C             |

|                                                    | B <sub>XY</sub> | 30           | -    | 70   | mT   | -40°C < T <sub>J</sub> <85°C              |

| Expanded Magnetic Induction at $T_A = 25$ °C 4) 5) | B <sub>XY</sub> | 25           | -    | 30   | mT   | Additional angle error of 0.1° 6)         |

| Angle Range                                        | Ang             | 0            | -    | 360  | 0    | Sine / cosine                             |

- 1) Directly blocked with 100-nF ceramic capacitor

- 2) Maximum current to GND over Open Drain Output

- 3) The corresponding voltage levels are listed in Table 5 and Table 6

- 4) Values refer to an homogenous magnetic field  $(B_{XY})$  without vertical magnetic induction  $(B_Z = 0mT)$

- 5) See Figure 7

- 6) 0h

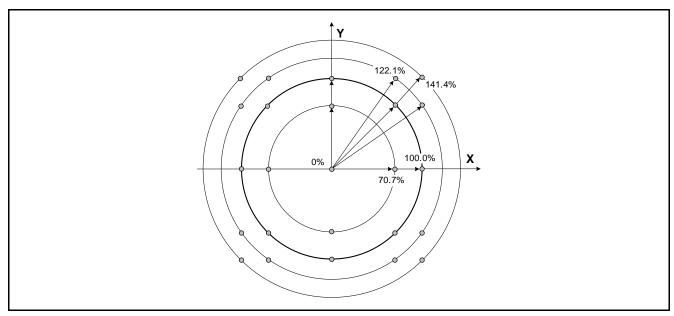

The field strength of a magnet can be selected within the colored area in **Figure 7**. By limitation of the junction temperature, a higher magnetic field can be applied. In case of a maximum temperature  $T_J = 100$ °C a magnet with up to 60mT at  $T_A = 25$ °C is allowed.

Figure 7 Magnet performance (ambient temperature)

Note: The thermal resistances listed in **Table 21 "Package Parameters" on Page 42** must be used to calculate the corresponding ambient temperature.

#### Calculation of the Junction Temperature

The total power dissipation  $P_{TOT}$  of the chip increases its temperature above the ambient temperature.

The power multiplied by the total thermal resistance  $R_{\rm thJA}$  (Junction to Ambient) leads to the final junction temperature.  $R_{\rm thJA}$  is the sum of the addition of the values of the two components *Junction to Case* and *Case to Ambient*.

$$\begin{split} R_{\text{thJA}} &= R_{\text{thJC}} + R_{\text{thCA}} \\ T_{\text{J}} &= T_{\text{A}} + \varDelta T \\ \varDelta T &= R_{\text{thJA}} \times \mathsf{P}_{\text{TOT}} = R_{\text{thJA}} \times \left( \ V_{\text{DD}} \times I_{\text{DD}} + V_{\text{OUT}} \times I_{\text{OUT}} \right) \\ I_{DD} \,, I_{OUT} &> 0, \, \text{if direction is into IC} \end{split}$$

Example (assuming no load on Vout):

- $-V_{\mathrm{DD}} = 5 \mathrm{V}$

- $-I_{\rm DD}$  = 15 mA

- $-\Delta T = 150$  [K/W] x (5 [V] x 0.015 [A] + 0 [VA] ) =11.25 K

For moulded sensors, the calculation with  $R_{\text{thJC}}$  is more adequate.

#### 3.4 Characteristics

#### 3.4.1 Electrical Parameters

The indicated electrical parameters apply to the full operating range, unless otherwise specified. The typical values correspond to a supply voltage  $V_{\rm DD}$  = 5.0 V and 25°C, unless individually specified. All other values correspond to - 40°C <  $T_{\rm J}$  < 150°C.

Table 4 Electrical Parameters

| Parameter         | Symbol                | Limit Va | Limit Values |                   |        | Notes                                                            |  |

|-------------------|-----------------------|----------|--------------|-------------------|--------|------------------------------------------------------------------|--|

|                   |                       | min.     | typ.         | max.              |        |                                                                  |  |

| Supply Current 1) | $I_{DD}$              | -        | 15           | 20                | mA     | $V_{\rm DD} = 3.0 \text{ to } 5.5 \text{V}$                      |  |

|                   |                       | -        | -            | 21                |        | V <sub>DD</sub> = 6.5 V                                          |  |

| POR Level         | $V_{POR}$             | 2.0      | 2.3          | 2.9               | V      | Power-On Reset                                                   |  |

| POR Hysteresis    | $V_{PORhy}$           | -        | 30           | -                 | mV     |                                                                  |  |

| Power-On Time     | t <sub>Pon</sub>      | 50       | 100          | 200               | μs     | $V_{\rm DD} > V_{\rm DDmin}$ & after first edge on $f_{\rm CLK}$ |  |

| PLL Jitter        | t <sub>PLLjit_S</sub> | -        | 1.3          | 2.0 <sup>2)</sup> | ns     | short term 3)                                                    |  |

|                   | t <sub>PLLjit_L</sub> |          | 3.0          | 3.9               |        | long term 4)                                                     |  |

| ADC Noise 5)      | $N_{ADC}$             | -        | 1            | 2.2               | digits | 1 σ @ FIR_BYP = 0                                                |  |

|                   |                       | -        | 2            | 4.4 <sup>2)</sup> |        | 1 σ @ FIR_BYP = 1                                                |  |

**Table 4** Electrical Parameters

| Parameter                      | Symbol      | Limit Valu          | Limit Values |                          |    | Notes                                                 |  |

|--------------------------------|-------------|---------------------|--------------|--------------------------|----|-------------------------------------------------------|--|

|                                |             | min.                | typ.         | max.                     |    |                                                       |  |

| Input Signal<br>Low Level      | $V_{L}$     | -0.35               | -            | 0.3 V <sub>DD</sub>      | V  | Tested only at DATA pin as structures of all pins are |  |

| Input Signal<br>High Level     | $V_{H}$     | 0.7 V <sub>DD</sub> | -            | V <sub>DD</sub><br>+0.35 | V  | identical                                             |  |

| Capacitance of SSC<br>Data Pin | $C_{LDATA}$ | -                   | 4            | 6 <sup>2)</sup>          | pF | Internal                                              |  |

- 1) Without external pull-up resistor for SSC interface

- 2) Not subject to production test verified by design/characterization

- 3) From pulse to pulse

- 4) Accumulated over 1 ms

- 5) ADC noise with respect to the peak ADC value specified in "Signal Processing" on Page 21. Noise tested using 1  $\sigma$  of 100 sample values from Angle Test "000"

Table 5 Electrical Parameters for 3.0V  $< V_{DD} < 3.6V$

| Parameter         | Symbol    | Limit Value          | Limit Values |      |    | Notes                                                                                               |

|-------------------|-----------|----------------------|--------------|------|----|-----------------------------------------------------------------------------------------------------|

|                   |           | min.                 | typ.         | max. |    |                                                                                                     |

| Input Hysteresis  | $V_{HY3}$ | 0.02 V <sub>DD</sub> | -            | -    | V  |                                                                                                     |

| Pull-Up Current   | $I_{PU3}$ | -5                   | -            | -50  | μA | CS, DATA                                                                                            |

| Pull-Down Current | $I_{PD3}$ | 10                   | -            | 150  | μA | SCK, CLK                                                                                            |

|                   |           | 8                    | -            | 100  |    | TST1                                                                                                |

|                   |           | 5                    | -            | 50   |    | TST2                                                                                                |

| Output Signal     | $V_{OL3}$ | -                    | -            | 1.3  | V  | $I_{\rm Q}$ = - 10 mA<br>$I_{\rm Q}$ = - 7 mA <sup>1)</sup><br>$I_{\rm Q}$ = - 2.5 mA <sup>1)</sup> |

| Low Level         |           | -                    | -            | 0.9  |    | $I_{\rm Q} = -7  {\rm mA}^{1)}$                                                                     |

|                   |           | -                    | -            | 0.4  |    | $I_{\rm Q}$ = - 2.5 mA <sup>1)</sup>                                                                |

<sup>1)</sup> Not subject to production test - verified by design/characterization

Table 6 Electrical Parameters for  $4.5V < V_{DD} < 5.5V$

| Parameter         | Symbol    | Limit Values         |           |      | Unit | Notes                                                       |

|-------------------|-----------|----------------------|-----------|------|------|-------------------------------------------------------------|

|                   |           | min.                 | min. typ. | max. |      |                                                             |

| Input Hysteresis  | $V_{HY5}$ | 0.07 V <sub>DD</sub> | -         | -    | V    |                                                             |

| Pull-Up Current   | $I_{PU5}$ | -10                  | -         | -150 | μA   | CS, DATA                                                    |

| Pull-Down Current | $I_{PD5}$ | 15                   | -         | 225  | μΑ   | SCK, CLK                                                    |

|                   |           | 15                   | -         | 225  |      | TST1                                                        |

|                   |           | 10                   | -         | 150  |      | TST2                                                        |

| Output Signal     | $V_{OL5}$ | -                    | -         | 0.7  | V    | I <sub>O</sub> = - 10 mA                                    |

| Low Level         |           | -                    | -         | 0.4  |      | $I_{\rm Q}$ = - 10 mA<br>$I_{\rm Q}$ = - 5 mA <sup>1)</sup> |

<sup>1)</sup> Not subject to production test - verified by design/characterization

### 3.4.2 ESD Protection

Table 7 ESD Protection

| Parameter   | Symbol    | Limit Values |       | Unit | Notes             |

|-------------|-----------|--------------|-------|------|-------------------|

|             |           | min.         | max.  |      |                   |

| ESD Voltage | $V_{HBM}$ | -            | ± 4   | kV   | HBM <sup>1)</sup> |

|             | $V_{SDM}$ | -            | ± 500 | V    | SDM <sup>2)</sup> |

<sup>1)</sup> Human Body Model (HBM) according to: AEC-Q100-002

### 3.4.3 GMR Parameters

All parameters apply over the full operating range, unless otherwise specified.

**Table 8** Basic GMR Parameters

| Parameter                | Symbol        | Limit Va  | alues |        | Unit   | Notes                        |  |

|--------------------------|---------------|-----------|-------|--------|--------|------------------------------|--|

|                          |               | min. typ. |       | max.   |        |                              |  |

| X, Y Output range        | $RG_{ADC}$    | -         | -     | ±23230 | digits |                              |  |

| X, Y Amplitude 1)        | $A_{X,}A_{Y}$ | 6000      | 9500  | 15781  | digits | at calibration conditions    |  |

|                          |               | 3922      | -     | 20620  |        | Operating Range              |  |

| X, Y Synchronism 2)      | k             | 80        | 100   | 120    | %      | at calibration conditions    |  |

| X, Y Offset 3)           | $O_{X},O_{Y}$ | -3000     | 0     | 3000   | digits | at calibration conditions    |  |

| X, Y Orthogonality Error | φ             | -10.0     | 0     | 10.0   | 0.0    | at calibration conditions    |  |

| X, Y without field       | $X_0, Y_0$    | -5000     | -     | 5000   | digits | without magnet <sup>4)</sup> |  |

<sup>1)</sup> See Figure 2

#### **Offset and Amplitude**

Figure 8 Offset and Amplitude Definition

<sup>2)</sup> Socketed Device Model (SDM) according to: ESDA/ANSI/ESD SP5.3.2-2008

<sup>2)</sup>  $k = 100 \text{ x} (A_X/A_Y)$ .

<sup>3)</sup>  $o_{\text{SIN}} = (Y_{\text{MAX}} + Y_{\text{MIN}}) / 2$ ;  $o_{\text{COS}} = (X_{\text{MAX}} + X_{\text{MIN}}) / 2$

<sup>4)</sup> Not subject to production test - verified by design/characterization

### **Offset Definition**

The offset of the X and Y signals is defined as the mean value between the signed maximum and minimum values of the idealized sine or cosine wave.

$$O_X = \frac{X_{\text{MAX}} + X_{\text{MIN}}}{2}$$

$$O_{\rm Y} = \frac{Y_{\rm MAX} + Y_{\rm MIN}}{2}$$

#### **Amplitude Definition**

The amplitude is defined as half the difference between the signed maximum and minimum values of the idealized sine or cosine wave.

$$A_{\rm X} = \frac{X_{\rm MAX} - X_{\rm MIN}}{2}$$

$$A_{\rm Y} = \frac{Y_{\rm MAX} - Y_{\rm MIN}}{2}$$

#### Temperature-dependent behavior

The temperature offset gradients for both channels depend on the value at 25°C. The gradients can be calculated using the following linear equations:

$$KT_{OX} = tco\_d\_x + (tco\_k\_x \times O_{X25})$$

$$KT_{OY} = tco\_d\_y + (tco\_k\_y \times O_{Y25})$$

O<sub>X25</sub>, O<sub>Y25</sub>: Offset values at 25°C in digits.

The application note "TLE5011 Calibration" describes in chapter 2.3, how to determine the coefficients ( $KT_{OX}$ ,  $KT_{OY}$ ).

#### **Orthogonality Definition**

The corresponding maximum and zero-crossing points of the SIN and COS signals do not occur at the precise distance of 90°. The difference between X and Y phase is called the **orthogonality error**.

$$\varphi = \varphi_X - \varphi_Y$$

$$\phi_{ideal} = 0^{\circ}$$

$\varphi_X$ : Phase error of X (= cos) signal

$\phi_Y$ : Phase error of Y (= sin) signal

#### 3.5 Calibration

#### **GMR Values**

The end-of-line calibration can be accomplished using following sequence:

- 1. Turn magnetic field 360° left and measure X and Y values

- 2. Calculate amplitude, offset, phase correction values of left turn

- 3. Turn further 90° left and 90° back right without measurement

- 4. Turn magnetic field 360° right and measure X and Y values

- 5. Calculate amplitude, offset, phase correction values of right turn

- 6. Calculate mean values of amplitude, offset, phase correction values

The conditions are specified in Table 9.

The values obtained from this sequence must be stored in a non-volatile memory. They are used for the correction of the read-out X and Y values before the angular calculation.

The resulting angular deviation is calculated using the parameters determined above.

#### **Temperature Measurement**

The signal amplitude  $T_{25}$  of the temperature measurement path at the calibration conditions must be measured and stored.

#### **Calibration Conditions**

All errors are related to calibration performed by Infineon under the following conditions:

Table 9 GMR test calibration conditions at IFX

| Parameter    | Symbol    | Limit Values |      |      | Unit | Notes                |

|--------------|-----------|--------------|------|------|------|----------------------|

|              |           | min.         | typ. | max. |      |                      |

| Flux density | $B_{CAL}$ | -            | 30   | -    | mT   | $B_Z = 0 \text{ mT}$ |

| Temperature  | $T_{CAL}$ | -            | 25   | -    | °C   |                      |

### 3.6 Angle Calculation

#### 3.6.1 Components of the Output Signals

The X and Y signals at the output can be described by the following equations:

$$X = A_X \times \cos(\alpha + \phi_X) + O_X$$

$$Y = A_{Y} \times \sin(\alpha + \phi_{Y}) + O_{Y}$$

$A_{\rm X}$ : Amplitude of X (= cos) signal  $A_{\rm Y}$ : Amplitude of Y (= sin) signal  $O_{\rm X}$ : Offset of X (= cos) signal  $O_{\rm Y}$ : Offset of Y (= sin) signal  $O_{\rm Y}$ : Phase error of X (= cos) signal  $O_{\rm Y}$ : Phase error of Y (= sin) signal

#### 3.6.2 GMR Error Compensation

#### **Temperature-dependent Offset Value**

To increase the accuracy, the temperature-dependent offset drift can be compensated. The temperature of the chip must be read out. The offset values  $O_X$  and  $O_Y$  can be described by the following equations.

$$O_{\rm X} = O_{\rm X25} + \frac{KT_{\rm OX}}{S_{\rm T}} \times (T - T_{25})$$

$$O_{\rm Y} = O_{\rm Y25} + \frac{KT_{\rm OY}}{S_{\rm T}} \times (T - T_{25})$$

O<sub>X25</sub> , O<sub>Y25</sub> : Offset value at 25°C in digits

T<sub>25</sub>: Temperature value at 25°C in digits

T: Temperature value in digits

S<sub>T</sub>: Sensitivity of the temperature measurement path, (see "Temperature Measurement" on Page 38).

#### **Offset Correction**

After the X and Y values are read out, the temperature-corrected offset value must be subtracted.

$$X_1 = X - O_X$$

$$Y_1 = Y - O_Y$$

#### **Amplitude Normalization**

Next, the X and Y values are normalized using the peak values determined in the calibration.

$$X_2 = \frac{X_1}{A_X}$$

$$Y_2 = \frac{Y_1}{A_Y}$$

#### **Non-Orthogonality Correction**

The influence of the non-orthogonality can be compensated using thefollowing equation, in which only the Y channel must be corrected.

$$Y_3 = \frac{Y_2 - X_2 \times \sin(-\varphi)}{\cos(-\varphi)}$$

#### **Resulting Angle**

After correction of all errors, the resulting angle can be calculated using the arctan function<sup>1)</sup>.

$$\alpha = \arctan\left(\frac{Y_3}{X_2}\right) - \varphi_X$$

<sup>1)</sup> Microcontroller function "arctan2(Y<sub>3</sub>,X<sub>2</sub>)" to resolve 360°

#### 3.6.3 GMR Parameters after Calibration

After calibration under the conditions specified in Table 9 "GMR test calibration conditions at IFX" on Page 19, the sensor has a remaining error as shown in Table 10.

The error value refers to  $B_Z = 0$  mT and operating conditions given in **Table 3 "Operating Range" on Page 14**.

Table 10 GMR Parameter with Temperature-Dependent Offset Compensation

| Parameter           | Symbol       | Limit | Limit Values       |      |   | Notes                                                     |  |

|---------------------|--------------|-------|--------------------|------|---|-----------------------------------------------------------|--|

|                     |              | min.  | typ. <sup>1)</sup> | max. |   |                                                           |  |

| Overall Angle Error | $lpha_{err}$ | -     | 0.7                | 1.6  | o | Including temperature drift 2) 3)                         |  |

|                     |              | -     | -                  | 2.2  | 0 | Including lifetime and temperature drift <sup>2) 4)</sup> |  |

<sup>1)</sup> At 25°C, B=30mT

- 2) Including hysteresis error

- 3) At 0h

- 4) Not subject to production test verified by design/characterization

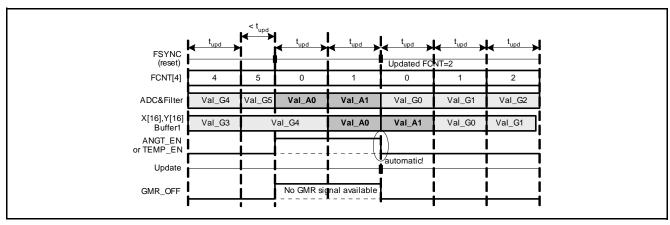

### 3.7 Signal Processing

Table 11 Signal Processing

| Parameter                                     | Symbol               | Limit Va | alues              |       | Unit   | Notes                                          |  |

|-----------------------------------------------|----------------------|----------|--------------------|-------|--------|------------------------------------------------|--|

|                                               |                      | min.     | typ. <sup>1)</sup> | max.  |        |                                                |  |

| Internal Cutoff                               | $f_{Cut\text{-Off}}$ | -        | 4.9                | -     | kHz    | FIR_BYP=0                                      |  |

| Frequency (-3dB) of sin or cos Value          |                      |          | 19.6               |       |        | FIR_BYP=1                                      |  |

| Update Time of sin or cos Value <sup>2)</sup> | $t_{\sf upd}$        | -        | 81.9               | -     | μs     | FIR_BYP=0                                      |  |

|                                               |                      | -        | 20.5               | -     |        | FIR_BYP=1                                      |  |

| Settle Time 3)                                | $t_{ m settle}$      | -        | 163.8              | -     |        | FIR_BYP=0                                      |  |

|                                               |                      | -        | 41.0               | -     |        | FIR_BYP=1                                      |  |

| Peak ADC Output value                         | $ADC_{Pk}$           | -        | -                  | 23230 | digits | Signed 16-bit integer (2s complement) 4) 5) 6) |  |

<sup>1)</sup> For 4-MhHz input frequency

- 4) Output values are valid up to this limit. Above it, corrupted results may occur due to non-linearity of the ADC.

- 5) One digit typically represents  $5.166 \,\mu V$

- 6) Corresponds to max. GMR output value

<sup>2)</sup>  $t_{upd} = 8192 / (25 \text{ x f}_{CLK}) \text{ for FIR\_BYP} = 0$  $t_{upd} = 8192 / (100 \text{ x f}_{CLK}) \text{ for FIR\_BYP} = 1$

<sup>3)</sup>  $t_{settle} = 2 x t_{upd}$ , after change of ADC input source

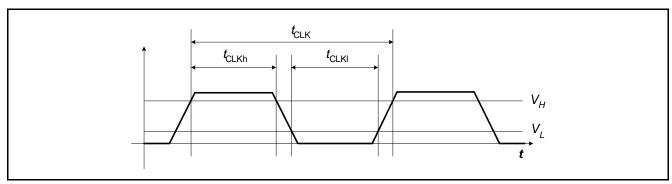

## 3.8 Clock Supply (CLK Timing Definition)

The clock signal input "CLK" must fulfill certain requirements described in this section:

- The high or low pulse width must not exceed the specified values, because the PLL needs a minimum pulse width and must be spike filtered.

- The duty-cycle factor should be 0.5 but can deviate from the values limited by  $t_{\text{CLKh(f min)}}$  and  $t_{\text{CLKl(f min)}}$ .

- The PLL is triggered at the positive edge of the clock. If more than 2 edges are missing, a chip reset is generated automatically.

Figure 9 CLK Timing Definition

| Parameter             | Symbol            | Limit Values |      |      | Unit | Notes                           |  |

|-----------------------|-------------------|--------------|------|------|------|---------------------------------|--|

|                       |                   | min.         | typ. | max. |      |                                 |  |

| Input Frequency       | $f_{CLK}$         | 3.8          | 4.00 | 4.2  | MHz  |                                 |  |

| CLK Duty Cycle 1)     | $CLK_{DUTY}$      | 30           | 50   | 70   | %    |                                 |  |

| CLK rise time         | t <sub>CLKr</sub> | -            | -    | 20   | ns   | from $V_{\rm L}$ to $V_{\rm H}$ |  |

| CLK fall time         | t <sub>CLKf</sub> | -            | -    | 20   | ns   | from $V_{\rm H}$ to $V_{\rm L}$ |  |

| PLL Frequency         | $f_{PLL}$         | -            | 100  | -    | MHz  | f <sub>CLK</sub> * 25           |  |

| Digital Clock         | $f_{DIG}$         | -            | 25   | -    | MHz  | (25/4)* f <sub>CLK</sub>        |  |

| Digital Clock Periode | $t_{DIG}$         | -            | 40   | -    | ns   | 4 / (25 * f <sub>CLK</sub> )    |  |

<sup>1)</sup> Minimum duty-cycle factor:  $t_{CLKh(f\_min)} / t_{CLK(f\_min)}$  with  $t_{CLK(f\_min)} = 1 / f_{CLK(f\_min)}$  Maximum duty-cycle factor:  $t_{CLKh(f\_max)} / t_{CLK(f\_min)}$  with  $t_{CLKh(f\_max)} = t_{CLK(f\_min)} - t_{CLKl(f\_min)}$

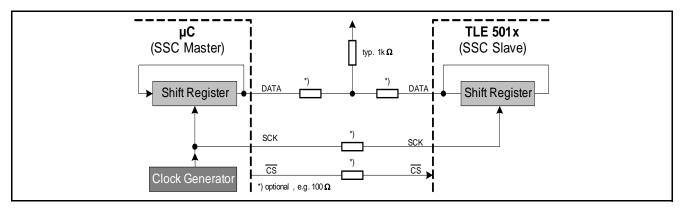

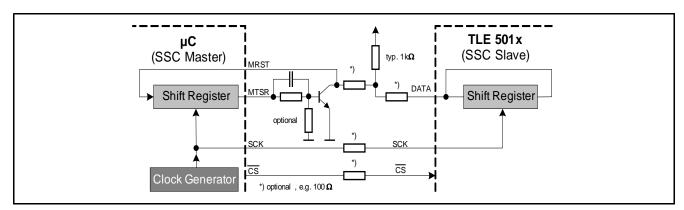

## 3.9 Synchronous Serial Communication Interface (SSC)

The 3-pin SSC interface has a bidirectional data line (open drain), a serial clock signal, and Chip Select.

The SSC interface is designed to communicate with a microcontroller with bi-directional SSC interface supporting open drain. Other microcontrollers may require an external NPN transistor.

This allows communication with SPI-compatible devices.

Figure 10 SSC Half-Duplex Configuration - Microcontroller with Open Drain

Figure 11 SSC Half-Duplex Configuration - Microcontroller without Open Drain

### 3.9.1 SSC Timing Definition

#### **SSC Timing Diagram**

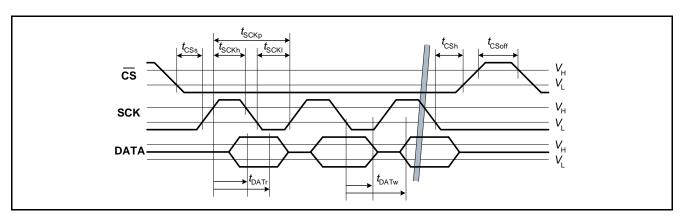

Figure 12 SSC Timing Definition

## SSC Inactive Time ( $\overline{CS}_{off}$ )

The SSC Inactive Time defines the delay before the TLE5011 can be selected again after a transfer. The TLE5011 reacts only to one command after an SSC Inactive Time. Then the SSC interface of the TLE5011 is disabled until the next SSC Inactive Time occurs.

#### DATA Write Time ( $t_{DATW}$ )

During this time, the TLE5011 changes the data line, so the data are invalid. The DATA Write Time values are defined without a pull-up resistor.

#### Pull-up Time Value ( $t_{PII}$ )

The value in Table 13 "SSC Timing Specification" on Page 24 is estimated at 60 ns.

Table 13 SSC Timing Specification

Note: Timing must be calculated according to Table 12 "CLK Timing Specification" on Page 22

| Parameter                               | Symbol             | Limit Value            | s    |                          | Unit     | Notes             |  |

|-----------------------------------------|--------------------|------------------------|------|--------------------------|----------|-------------------|--|

|                                         |                    | min.                   | typ. | max.                     |          |                   |  |

| SSC Baud Rate                           | $f_{SSC}$          | -                      | 2.0  | 2.1 <sup>1)</sup>        | Mbit / s |                   |  |

| CS Setup Time                           | $t_{\mathrm{CSs}}$ | 3*t <sub>DIG</sub> +10 | -    | -                        | ns       |                   |  |

| CS Hold Time                            | $t_{CSh}$          | 5*t <sub>DIG</sub> +10 | -    | -                        | ns       |                   |  |

| <del>CS</del> <sub>off</sub>            | $t_{CSoff}$        | 10*t <sub>DIG</sub>    | -    | -                        | ns       | SSC inactive time |  |

| SCK High                                | t <sub>SCKh</sub>  | 5*t <sub>DIG</sub>     | -    | -                        | ns       |                   |  |

| SCK Low                                 | t <sub>SCKI</sub>  | 5*t <sub>DIG</sub>     | -    | -                        | ns       |                   |  |

| DATA Read Time                          | $t_{DATr}$         | 6*t <sub>DIG</sub> -10 | -    | 7*t <sub>DIG</sub> +10   | ns       | SSC_FILT = 0      |  |

| (Data Valid Time)                       |                    | 5*t <sub>DIG</sub> -10 | -    | 7*t <sub>DIG</sub> +10   |          | SSC_FILT = 1      |  |

| DATA Write Time<br>(Data Valid Time) 2) | $t_{DATw}$         | 6*t <sub>DIG</sub> +25 | -    | $7^*t_{DIG}+50 + t_{PU}$ | ns       |                   |  |

| DATA slope                              | $t_{DATs}$         | -                      | 20   | 30 <sup>3)</sup>         | ns       | Falling edge 4)   |  |

- 1)  $f_{CLK}/2$ , synchronized to  $f_{CLK}$  if  $fCLK = f_{CLK}(max)$

- 2) tpul is the time generated by the pull-up resistor

- 3) Not subject to production test verified by design/characterization

- 4) Internal slope control of falling edge for data bit transition from  $V_{\rm H}$  to  $V_{\rm I}$ .

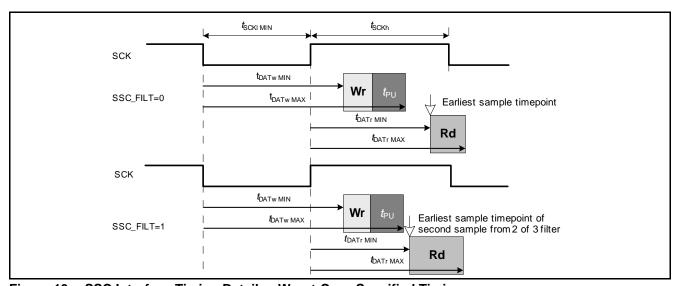

Figure 13 SSC Interface Timing Details - Worst-Case Specified Timing

Note: The read window includes the sampling of the data bit. For SSC\_FILT = 1, the 2-of-3 selection is already considered. Only the two last data values need to be equal. For SSC\_FILT = 0, only one sample point is selected.

The margin time shown in **Table 14** is the time between write access to the SSC data line and the earliest possible sample read of the TLE5011 itself for read-back.

It is useful to have a maximum distance between the WRITE and subsequent READ. This ensures a reliable readback of the written data for the Slave-Active Byte generation.

Table 14 Maximum Pull-up Time Margin with Worst-Case Specified Timing

| SSC_FILT | SSC_TIMING | Min. t <sub>PU</sub> Margin <sup>1)</sup> | Unit | Comment |

|----------|------------|-------------------------------------------|------|---------|

| 0        | don't care | 90                                        | ns   |         |

| 1        |            | 50                                        |      |         |

<sup>1)</sup> Calculation: Margin=t<sub>SCKI(min)</sub>+t<sub>DATwMAX</sub>-(t<sub>PU</sub>)-t<sub>DATrMIN</sub>.For Margin<50 ns no problems can occur.

#### 3.9.2 SSC Baud rate

The SSC baud rate depends on the internal clock frequency.

Twelve internal digital clock cycles are necessary to ensure reliable operation. Therefore, the maximum SSC baud rate depends on the external CLK.

$$f_{SSC} = \frac{f_{CLK}}{2}$$

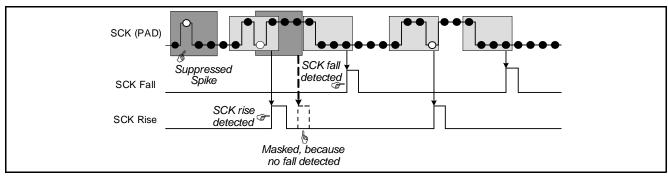

#### 3.9.3 SSC Spike Filter

A spike filter for all SSC lines can be selected via the SSC\_FILT bit.

#### SSC Spike Filter Off

When the spike filter is disabled, each slope with rising voltage is used to define a bit. This is independent of the length of the sampled pulse. For example, a positive spike generates a rising and a falling edge.

#### SSC Spike Filter On

A sliding window with four consecutive sample bits is analyzed.

The sample frequency is:

$$f_{\rm S} = \frac{1}{f_{\rm DIGIT}}$$

### Rising Edge Detect for SCK

- After a rising edge (LH combination), at least one of the two following samples must be high. Valid bit combinations: 0111, 0110, 0101.

- A falling condition must be detected previously.

#### **Falling Edge Detect for SCK**

- After a falling edge (HL combination), at least one of the two following samples must be low. *Valid bit combinations: 1000*, 1001, 1010.

- · A rising condition must be detected previously.

Figure 14 SSC Spike Filter

#### Filter for DATA and CS

The following conditions apply:

- The DATA pin has a '2-of-3' filter

- The CS input has a '2-of-3' filter that suppresses only positive spikes

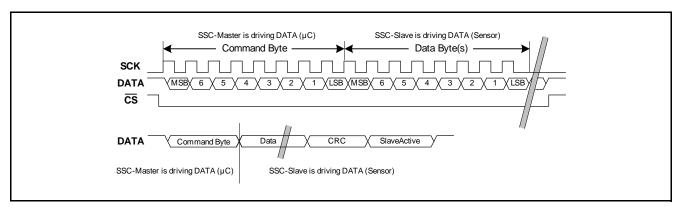

#### 3.9.4 SSC Data Transfer

The following transfer Byte are possible:

- Command Byte (to access and change operating modes of the TLE5011)

- Data Bytes (any data transferred in any direction)

- CRC Byte (cyclic redundancy check)

- Slave-active Byte (response of all selected slaves)

Figure 15 SSC Data Transfer (Data Read Example)

### 3.9.5 SSC Command Byte

The TLE5011 is controlled by a command Byte. It is sent first at every data transmission.

Table 15 Structure of the Command Byte

| Name | Bits | Description                                                      |

|------|------|------------------------------------------------------------------|

| RW   | [7]  | Read - Write                                                     |

|      |      | 0 = write, 1 = read                                              |

| ADDR | [63] | Address to be read / written                                     |

|      |      | 015 - register start address (address auto increment)            |

| ND   | [20] | Number of data Bytes 07 - number of data Bytes to be transferred |

### **Register Table**

This section describes the complete address range as well as all registers of the TLE5011. It also defines the read/write access rights of the specific registers. **Table 16** identifies the values with symbols. Access to the registers is accomplished via the SSC interface.

Table 16 Address Map

| Addr.           | Name          | Bits         |                 |                            |                   |              |             |             |              |

|-----------------|---------------|--------------|-----------------|----------------------------|-------------------|--------------|-------------|-------------|--------------|

|                 |               | 7            | 6               | 5                          | 4                 | 3            | 2           | 1           | 0            |

| 00 <sub>H</sub> | CTRL1         | -            | -               | -                          | -                 | SSC_<br>FILT | -           | AUTO        | UR           |

| 01 <sub>H</sub> | XL            |              |                 |                            | $X_{Low}$         | v            |             |             |              |

| 02 <sub>H</sub> | XH            |              |                 |                            | X <sub>High</sub> |              |             |             |              |

| 03 <sub>H</sub> | YL            |              |                 |                            | Y <sub>Low</sub>  |              |             |             |              |

| 04 <sub>H</sub> | YH            |              |                 |                            | $Y_{High}$        | h            |             |             |              |

| 05 <sub>H</sub> | FCNT_<br>STAT | -            | STAT_<br>VR     | GMR_<br>OFF                | UPDATE            | FCNT         |             |             |              |

| 06 <sub>H</sub> | FSYNC_IN<br>V | FILT_<br>INV |                 | FSYNC                      |                   |              |             |             |              |

| 07 <sub>H</sub> | ANGT          | -            | ANGT_E<br>N     |                            | ANGT_Y            |              |             | ANGT_X      |              |

| )8 <sub>H</sub> | -             |              |                 |                            | reserv            | red          |             |             |              |

| )9 <sub>H</sub> | -             |              |                 |                            | reserv            | red          |             |             |              |

| )A <sub>H</sub> | -             |              |                 |                            | reserv            | red          |             |             |              |

| )B <sub>H</sub> | -             |              |                 |                            | reserv            | red          |             |             |              |

| OC <sub>H</sub> | TST           | TEMP_E<br>N  | ADCPY           | FILT_<br>PAR               | FILT_<br>CRS      | FILT_<br>BYP | TST_<br>ADC | TST_<br>GMR | TST_<br>CHAN |

| DD <sub>H</sub> | ID            |              | DEV_ID reserved |                            |                   |              |             |             |              |

| )E <sub>H</sub> | LOCK          |              |                 | LOCK                       |                   |              |             |             |              |

| OF <sub>H</sub> | CRTL2         | VDD_OV       | VDD_<br>OFF     | D_ GND_OF VRG_ VRA_ VRD_ , |                   |              |             | S_          | NO           |

### **Bit Types**

The types of bits used in the registers are listed here:

| Abbreviation | Function | Description                                                                                                                                                                                                                                                              |

|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L            | Locked   | Locked register.  Locked registers can be written only when the unlock-value is written in the lock register ( <b>0E</b> <sub>H</sub> ).  This ensures that these bits cannot be modified unintentionally during normal operation.                                       |

| U            | Update   | Update buffer for this bit is present.  If an Update Command is issued and the Update-Mode bit (UR in CTRL1) is set, the immediate values are stored in this Update Buffer simultaneously.  This enables a snapshot of all necessary system parameters at the same time. |

| Abbreviation Function |       | Description              |

|-----------------------|-------|--------------------------|

| S Status              |       | Reset only after readout |

| R                     | Read  | Read-only registers      |

| W                     | Write | Read and write registers |

CTRL1

Addr: 00<sub>H</sub> Reset Value: 01<sub>H</sub>

| 7        | 6        | 5        | 4        | 3        | 2        | 1    | 0  |

|----------|----------|----------|----------|----------|----------|------|----|

| reserved | reserved | reserved | reserved | SSC_FILT | reserved | AUTO | UR |

| -        | -        | -        | WL       | WI       | -        | WL   | WL |

| Field    | Bits                             | Туре | Description                                                                                                                                                                                                                                                                                              |

|----------|----------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reserved | 7                                | -    | Reserved, must be set to 0                                                                                                                                                                                                                                                                               |

| reserved | 6                                | -    | Reserved, must be set to 0                                                                                                                                                                                                                                                                               |

| reserved | 5                                | -    | Reserved, must be set to 0                                                                                                                                                                                                                                                                               |

| reserved | 4                                | -    | Reserved, must be set to 0                                                                                                                                                                                                                                                                               |

| SSC_FILT | 3                                | W L  | SSC Digital Spike Filter enable for all SSC lines ( \overline{CS}, CLK and DATA )  0: Digital SSC Spike filters off  1: Digital SSC Spike filters on (modified timing)                                                                                                                                   |

| reserved | 2                                | -    | Reserved, must be set to 0                                                                                                                                                                                                                                                                               |

| AUTO     | AUTO 1 W L Au 0: 1 : coi (Al ope |      | Automatic update at angle tests 0: no automatic update in Angle Test Mode 1: automatic update-command after $t_{\text{settle}}$ , counters FSYNC and FCNT are reset to 0. Then the Angle-Test (ANGT_EN) is automatically disabled and switches back to normal operation. Also, the UPDATE bit is toggled |

| UR       | 0                                | WL   | Update / Run Mode 0: Run Mode (Buffer1 values are immediate values) 1: Update Mode (Buffer2 values are stored values)                                                                                                                                                                                    |

The values in Register 01H to 04H represent one Byte of two's complement signed 16 bit integer values.

$X_L$

Addr: 01<sub>H</sub> Reset Value: 00<sub>H</sub>

7 6 5 4 3 2 1 0

X Low Byte

$X_H$

Addr: 02<sub>H</sub> Reset Value: 00<sub>H</sub>

| 7 | 6  | 5 | 4     | 3      | 2 | 1 | 0 |  |  |

|---|----|---|-------|--------|---|---|---|--|--|

|   | I  | ı | X Hig | h Byte | I | I | I |  |  |

|   | RU |   |       |        |   |   |   |  |  |

FCNT\_STAT

**Specification**

| _L                   |   |   | 5 414    |                       |          |   |    |

|----------------------|---|---|----------|-----------------------|----------|---|----|

| ddr: 03 <sub>H</sub> |   |   | Reset Va | alue: 00 <sub>H</sub> |          |   |    |

| 7                    | 6 | 5 | 4        | 3                     | 2        | 1 | 0  |

| '                    |   | ı | Y Lov    | w Byte                |          | 1 | 1  |

|                      |   | 1 | R        | Ü                     |          | 1 | -1 |

| _H                   |   |   |          |                       |          |   |    |

| ddr: 04 <sub>H</sub> |   |   | Reset Va | alue: 00 <sub>H</sub> |          |   |    |

| 7                    | 6 | 5 | 4        | 3                     | 2        | 1 | 0  |

| '                    |   | ' | Y Hig    | h Byte                |          | ' | '  |

| 1                    |   | 1 |          | : <sup>'</sup> U      | <u> </u> |   | 1  |

| Addr: 05 <sub>H</sub> |         |         | Reset Va | alue: 80 <sub>H</sub> |    |    |     |

|-----------------------|---------|---------|----------|-----------------------|----|----|-----|

| 7                     | 6       | 5       | 4        | 3                     | 2  | 1  | 0   |

| reserved              | STAT_VR | GMR_OFF | UPDATE   |                       | FC | NT | 1   |

| -                     | RS      | RU      | RS       |                       | R  | U  | 11. |

| Field    | Bits | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reserved | 7    | -    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| STAT_VR  | 6    | RS   | Voltage Regulator Status This bit is a logical OR combination of Digital, Analog, GMR and VDD_OV Comparator and GND_OFF, and VDD_OFF Comparator outputs.  0: Voltage Supply OK 1: Voltage Supply is not OK                                                                                                                                                                                                                                                                                                          |

| GMR_OFF  | 5    | RU   | ADC Values are no GMR values (e.g.: Temperature measurement is active) This bit indicates whether or not GMR values or any other values are connected to the ADCs. This value is read back from the multiplexer control signals. 0: X,Y Values are GMR values 1: X,Y Values normally represent temperature measurement or angle test values. In the case of non-functional MUX, this bit is set to 1                                                                                                                |

| UPDATE   | 4    | RU   | Update Toggle bit. This bit toggles after every update (update command or automatic update at angle test) The bit is independent of UR bit in CTRL1                                                                                                                                                                                                                                                                                                                                                                 |

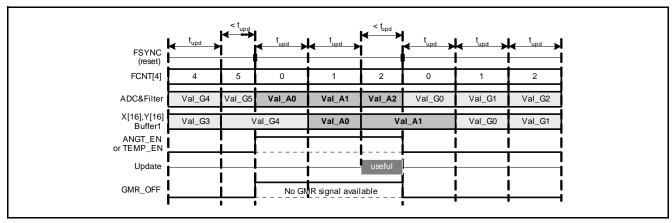

| FCNT     | 3-0  | RU   | Frame Counter (4-bit unsigned integer value) This counter counts every new X,Y value pair coming out of the data path. (approx. $80\mu s$ ) This counter is reset to $0_H$ after any write to FSYNC and after every change of the ANGT_EN bit. As $t_{settle}$ time has to elapse for valid X,Y data, this counter must be $\geq 2_H$ to indicate valid X,Y values. If it overflows, it resets to $3_H$ to show that values are still valid.  Note: If FIR BYP is activated, this counter counts four times faster! |

| FS | ΥN | IC | INV |

|----|----|----|-----|

|    |    |    |     |

| Addr: 06 <sub>H</sub> |   |   | Reset Va | alue: 00 <sub>H</sub> |   |   |  |

|-----------------------|---|---|----------|-----------------------|---|---|--|

| 7                     | • | _ | 4        | 2                     | 0 | 4 |  |

|          | _ |  |       |  |  |

|----------|---|--|-------|--|--|

| FILT_INV |   |  | FSYNC |  |  |

| WU       |   |  | WU    |  |  |

| Field    | Bits | Туре | Description                                                                                                                                                                                                                                                                           |

|----------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FILT_INV | 7    | WU   | Filter Input Inversion (to check the digital data path during operation) 0: Filter Inputs are not inverted 1: Filter Inputs are inverted                                                                                                                                              |

| FSYNC    | 6-0  | WU   | Frame Synchronization (7-bit unsigned integer value) The Filter Update time of approx. 80 µs results from the filter decimation. The phase of this decimation can be set and checked by this counter.  If FIR_BYP is activated, this counter overflows at the value 31 <sub>D</sub> . |

#### **ANGT**

Addr: 07<sub>H</sub> Reset Value: 00<sub>H</sub>

|   | 7        | 6       | 5 | 4      | 3 | 2 | 1      | 0 |

|---|----------|---------|---|--------|---|---|--------|---|

|   | reserved | ANGT_EN |   | ANGT_Y |   |   | ANGT_X |   |

| • |          | W       |   | W      |   |   | W      |   |

| Field    | Bits | Туре | Description                                                                                                                                                                        |

|----------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reserved | 7    | -    | Reserved, must be set to 0                                                                                                                                                         |

| ANGT_EN  | 6    | W    | Angle Test Enable 0: Angle Test disable command 1: Angle Test enable command in this case X and Y values represent resistive test values that can be used to simulate angle values |

| ANGT_Y   | 5-3  | W    | Angle Test X and Y value                                                                                                                                                           |

| ANGT_X   | 2-0  | W    | See : Table 18 "Functional Angle Test" on Page 37                                                                                                                                  |

## Reserved Registers (08<sub>H</sub> to 0B<sub>H</sub>)

The values in these registers are 8-bit unsigned integer values.

The values in addr.8 and addr.9 have to be in reset status.

### Reserved

Addr: 08<sub>H</sub> Reset Value: FF<sub>H</sub>

| 7        | 6   | 5 | 4 | 3 | 2 | 1  | 0 |  |  |

|----------|-----|---|---|---|---|----|---|--|--|

|          |     | Т | D |   | I | I  | П |  |  |

| Reserved |     |   |   |   |   |    |   |  |  |

|          | II. | 1 | I | 1 | I | İI | 1 |  |  |

Reserved

Addr: 09<sub>H</sub> - 0B<sub>H</sub> Reset Value: 00<sub>H</sub>

| 7 | 6 | 5 | 4    | 3     | 2  | 1 | 0 |

|---|---|---|------|-------|----|---|---|

|   |   | I | Rese | erved |    | I |   |

| 1 |   | İ | I.   | ı     | Ť. | 1 | 1 |

**TST**

Addr: 0C<sub>H</sub> Reset Value: 00<sub>H</sub>

| 7       | 6     | 5        | 4        | 3       | 2       | 1       | 0            |

|---------|-------|----------|----------|---------|---------|---------|--------------|

| TEMP_EN | ADCPY | FILT_PAR | FILT_CRS | FIR_BYP | TST_ADC | TST_GMR | TST_<br>CHAN |

| WL      | WL    | WL       | WL       | WL      | WL      | WL      | WL           |

| Field      | Bits | Туре | Description                                                                                                                                                                       |

|------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEMP_EN    | 7    | W L  | Temperature Device Enable 0: Temperature Measurement disabled 1: Temperature Measurement enabled The X value represents the temperature. Automatic update mode enabled, if AUTO=1 |

| ADCPY      | 6    | W L  | Y Polarity 0: No inversion of Y bitstream 1: Inversion of Y bitstream (rotating direct. changed)                                                                                  |

| FILT_PAR   | 5    | WL   | Filter switched parallel 0: Filters in normal mode 1: Filters parallel, input selected by TST_CHAN                                                                                |

| FILT_CRS   | 4    | W L  | Filter switched across 0: Filters in normal mode 1: Filters crossed, X and Y outputs are exchanged                                                                                |

| FIR_BYP    | 3    | W L  | FIR Filter Bypass 0: No FIR Bypass 1: FIR Bypass                                                                                                                                  |

| TST_ADC 1) | 2    | W L  | ADC input switch to TST1and TST2  0: No ADC input switch, normal operation  1: ADC input switched to TST1,2, ADC selected by TST_CHAN <sup>2)</sup>                               |

| TST_GMR 1) | 1    | W L  | GMR switch to TST1and TST2 0: No GMR switch, normal operation 1: GMR switched to TST1,2 selected by TST_CHAN <sup>2)</sup>                                                        |

| TST_CHAN   | 0    | W L  | Test Channel select 0: X channel linked to TST1and TST2 1: Y channel linked to TST1and TST2                                                                                       |

<sup>1)</sup> Only for test purposes

<sup>2)</sup> if TST\_ADC and TST\_GMR are set to 1 at the same time, TST\_GMR is forced to 0. TST\_ADC has the higher priority.

| _ |

|---|

|   |

|   |

|   |

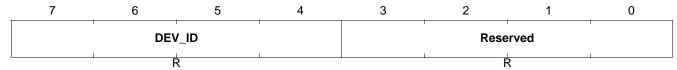

| Field    | Bits | Туре | Description                                                  |

|----------|------|------|--------------------------------------------------------------|

| DEV_ID   | 7-4  | R    | Device Identifier 001 <sub>H</sub> : TLE5011 production chip |

| reserved | 3-0  | -    |                                                              |

#### LOCK

Addr: 0E<sub>H</sub> Reset Value: 00<sub>H</sub>

| 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---|---|---|----|----|---|---|---|

|   | I | I | LO | CK | I | 1 |   |

|   | i | İ | I  | 1  | 1 | ı | İ |

|   |   |   | V  | V  |   |   |   |

| Field | Bits | Туре | Description                                                                                           |

|-------|------|------|-------------------------------------------------------------------------------------------------------|

| LOCK  | 7-0  | W    | Lock Byte<br>≠ 5A <sub>H</sub> : Lock registers locked<br>= 5A <sub>H</sub> : Lock registers unlocked |

### CTRL2

Addr: 0F<sub>H</sub> Reset Value: 00<sub>H</sub>

| 7      | 6       | 5       | 4      | 3      | 2      | 1  | 0  |

|--------|---------|---------|--------|--------|--------|----|----|

| VDD_OV | VDD_OFF | GND_OFF | VRG_OV | VRA_OV | VRD_OV | S_ | NO |

| R S    | R S     | R S     | R S    | R S    | R S    | W  | L  |

| Field   | Bits | Туре | Description                                                                                                               |

|---------|------|------|---------------------------------------------------------------------------------------------------------------------------|

| VDD_OV  | 7    | RS   | V <sub>DD</sub> Overvoltage Comparator 0: No V <sub>DD</sub> Overvoltage occurred 1: V <sub>DD</sub> Overvoltage occurred |

| VDD_OFF | 6    | RS   | $V_{\rm DD}$ - off Comparator 0: No $V_{\rm DD}$ - off occurred 1: $V_{\rm DD}$ - off occurred                            |

| GND_OFF | 5    | RS   | GND - off Comparator 0: No GND - off occurred 1: GND - off occurred                                                       |

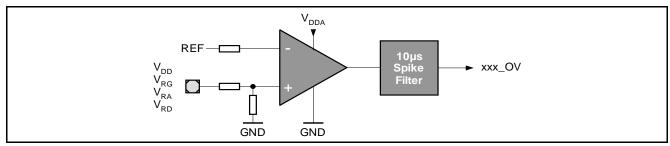

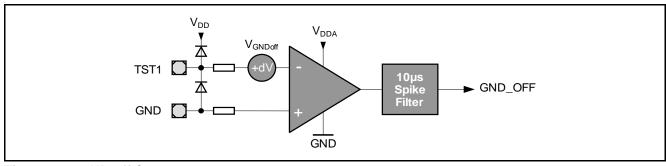

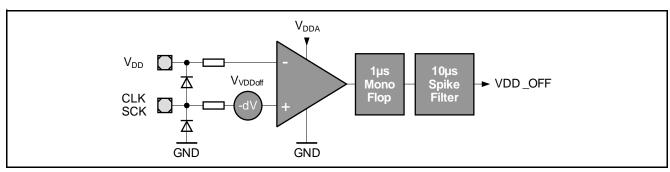

| VRG_OV  | 4    | RS   | GMR Voltage Regulator Overvoltage Comparator 0: Voltage ok 1: VRG Overvoltage occurred                                    |